# Low-Power Dynamic Comparator Design with Cascaded Architecture for Noise Minimization

1 Maradani Rajitha laxmi, Assistant Professor, Department of ECE, Ramachandra College of Engineering, Eluru, Email: rajitha281213@gmail.com

#### Abstract—

This work proposes a novel low-power dynamic comparator architecture employing a cascaded structure to effectively minimize noise while maintaining high-speed operation. The design integrates multiple amplification stages in a cascaded configuration, which enhances signal gain and suppresses input-referred noise without significantly increasing power consumption. By leveraging dynamic operation principles, the comparator achieves low static power dissipation and improved energy efficiency compared to conventional static comparators. Simulation results demonstrate that the proposed comparator achieves faster decision times, reduced offset voltage, and superior noise performance under various process and temperature variations. This architecture is particularly suitable for applications in high-resolution analog-to-digital converters (ADCs) and low-voltage mixedsignal integrated circuits, where low power and high precision are critical requirements.

# Keywords— Low-Power Design, Dynamic Comparator, Cascoded Structure, Noise Minimization.

### I.INTRODUCTION

Todaythisemergingneedforlow-power, high-speedanalog- todigital converters has promoted the development of new comparators. Comparators being a critical component of the ADCsaffecttheentirepowerconsumption, processing speed, andaccuracyoftheconverters. Traditional staticcomparators, however, sufferfrom excessive power consumption, restricted speed, and are very susceptible to noise. Recently, dynamic comparatorshavebeen ofconsiderableinterestinlow-power and high-speed applications. Dynamic comparators make use of a dynamic logic where the output is produced during the evaluation phase, and so the static power is minimal. Cascoded dynamic comparator was designed to increase its noiseimmunitywithoutreallyaffectingitsspeed,thusmaking itanidealconsiderationtoapplicationswhereaccuracyhasto be power-efficient in itself. This controlled noise-holding mechanismtakesintoconsiderationthethresholdvoltagesand transistor sizes for each cascoded stage resulting in even greater precision during adverse conditions. The new architecture marks a step forward in dynamic comparator design,promisingagoodsolutionformodernlow-powerbut high-performing analog-to-digital conversion systems. The cascoded dynamic comparator thus exhibits excellent noise immunity and high-speed performance, alongside improved robustness against process variations, temperature changes, and supplyvoltage fluctuations, which is criticalin high-performance analog-to-digital conversion systems, as even minutechanges can causelargeerrors. Itispreciselyin thatarea wherethisdesign ishelpful sinceit promises better performanceunderavarietyofoperatingconditions, making sure that the comparator remains reliable and consistent in performance over time.

#### II. PROPOSEDDYNAMICDESIGN

Thelow-dynamiccomparatordesigned and created is through cascaded structure that leads to maximum noise reduction power economyin thedemand ofhigh performanceandlow power consumption nowadays in modern electronic systems inthefieldofanalog-to-digitalconversion. The design of the cascoded double-tail architecture provides high gain and reduces noise sensitivity without compromising on the speed of response with optimum energy consumption. This cascoded effectivelyisolatesthenoise configuration whichaddstotheaccuracyandreliabilityofthiscomparator. Additionally, thecarefulsizingoftransistorsinthedifferential amplifier (DA) and the appropriate threshold voltage tuning of the tail transistor minimizes dynamic power dissipation, thereby improving the overall energy efficiency of the comparator.

Alsoessentialaboutthisapproachisreducedturn-onduration for the tail transistor, such that the comparator can operate even withminimumpowerloss. Thismeansimprovementin energy efficiency, and also in reducing the susceptibility to noise since the comparator continuously performs under different input conditions. The design of parasitic capacitancesat significant positions has been perfected, thus contributing highergain and fasters witching speeds, creating even more advantages for the comparator in high-speed applications. This design goes a long way in making the proposed comparator suitable for low-power high-speed circuits, right in the middle of performance, power consumption, and no is eimmunity that would be comecrucial for future systems analog and mixed-signal.

The design aims at optimizing the sizes of the transistors in the differential amplifier (DA) and adjusting the threshold voltage of the tail transistor. This optimization decreases dynamic power dissipation and thus improves energy efficiency in a way that keepsthetotal speedperformance of the comparator because the tail transistor is turned on for shorter duration.

Reducing the power losses during operation by a shorter switching schedule for the tail transistor results in greater overall power efficiency but without compromising speed. Incorporating further enhanced parasitic capacitance management at various critical positions gives an improvement in performance features, faster switching speeds, and gaining capability. This makes the comparator an excellent choice for high-speed analog-to-digital conversion

applications requiring high-resolution, high-speed conversion withpower efficiency. Thisdesignachievesadelicatebalance betweenlowpower,highspeed,andnoiseimmunitysoitwill be one of the best candidates for future low-power high performance in analog and mixed-signal systems. In the future, this paradigm would be useful as electronic systems become more complex so that comparators can be driven towardthe futurehigh-performancerequirementsof advanced systems.

#### III. SIMULATIONRESULTS

This comparator has been designed and implemented in the UMC 130nm CMOS process with low power for the comparator. However, the device is optimized for performanceatalowsupplyvoltageof1.2Vandconsumesa minimumamountofpower. This comparator can operate with a clock frequency of upto 1 GHz, so it can be used invery fast applications. This combination of low voltage and high-frequency making it an ideal balanced point of energy-saving speed meets requirements for modern electronic systems.

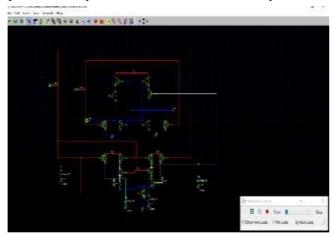

Fig1:Transientresponseoftheproposedcomparator

The process variation in source to body voltage is a factor that causes variations in the threshold voltage of NMOS of a chosen process. In this process, the maximum V thnisk nown to appear at the minimum VSB. Thus, for low power operation is selected as VDD. The proposed comparator delay is determined using Monte Carlo simulations.

The given image is a circuit schematic designed using electronic design automation (EDA) software, probably for simulating or analyzing an electronic circuit. The schematic contains many components such as transistors, resistors, capacitors, and connections highlighted with colored lines, representingsignalpathsorpower supplies. Thered, blue, and white lines might indicate different signal levels, nodes, or circuitpathsfordebuggingorsimulationpurposes. Thiskind ofschematicisusuallyusedforthedesignofanalogordigital verification of functionality, and simulation to predict circuits, circuit behavior under different conditions. The software alsoincludes tools such as a "Simulation Control" panel, where users can initiate simulations, view waveforms, or analyze circuitparameterslikevoltageandcurrentatdifferentnodes. Please let me know if you would like a more detailed explanation of the circuit or its parts.

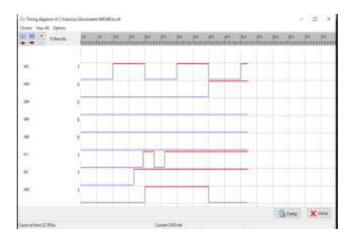

Fig2: The imagegiven shows a timing diagram with several signal names assigned to d1, d3, d4, etc. and corresponding transitions with time.

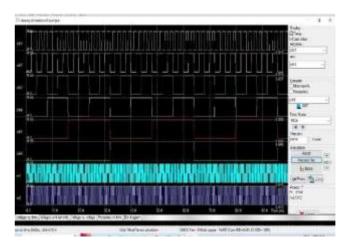

Fig3:Thegiven imageisa timing or waveform diagramthat iscommonlyusedindigital electronicstoanalyzeanddebug circuits or digital signals.

Itshowsseveralchannels(ch0,ch1,etc.),eachrepresentinga signal that switches between high (logic1)andlow(logic0) statesovertime. The top most signal is a clock pulse, which is often used to synchronize operations in digital systems. Such diagrams are particularly important for understanding temporal dependencies between signals, verifying the appropriate functionality of circuits, as well as analyzing protocols in SPI, I2C, or UART. Therefore, this output most likely comes from simulation tools Model Sim, Cadence or hardware devices such as logicanalyzer or an oscilloscope.

These tools serve to help engineers visualize and debug the behavior of digital systems by interpreting data transfer problems, synchronization problems, or simply timing problems in communication systems or control systems. Let me know if you want me to elaborate on any of the parts of the waveform further.

Theproposeddesignwillbeabletoconfrontsuchchallenges providing a considerably higher degree of stability and reliability acrossa widerange of conditions. Thestability of thecomparator can thus be maintained under process variation orchangingenvironmentalconditionsovertime. This type of comparatorhasacascodeddynamicstructurethatisuniquein terms of its very high-speed performance and outstanding noise immunity, which makes it suitable for the most advancedanaloguetodigitalconversionapplications. One of its most important strengths lies in itsreproducibility over a wide range of common environmental and operational conditions, such asprocess change, temperature change, and supplyvoltagefluctuations.Inhigh-speedADCsystems,even tiny deviations in these parameters can result in very large errors, which are unwelcome penalties for system performance.

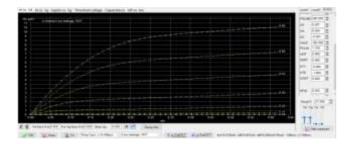

ThisistheIdvs VdsMOSFET characteristicgraph showing the operation of the device as Vgs changes. The curve demonstrates a linear increase in conductance and then the MOSFEThasmorecurrent drainIdforanyparticularvalueof Vds when the voltage Vgs is increased. The curve for MOSFET demonstrates saturation, linear, and pinch-off regions. Id becomes insensitive toVdswithan almost linear dependency on Vgs in the saturation region. In the linear region,IdversusVdsexhibitsalinearrelationship,indicating the MOSFET behaves like a voltage-controlled resistor. Beyond pinch-off lies the saturation region where saturation occursagain. Theimportantfeaturesarethresholdvoltageand channel length modulation with some increase in the saturation region because the effective channel length is decreased as Vds increases.

## IV. CONCLUSION

Thispaperpresentsanewlatch-typecomparatorarchitecture designedfornoiselessandlow-power operation, as expected for submicron CMOS technologies and compact power-efficient applications. In this regard, within the preamplifier stage, a cascode structure has been designed, which effectively enhances gain while reducing input referred noise and improving the overall performance of the comparator itself. While this cascode structure provides much betternoise immunity and gain, the cost for this imposes an increase in average power dissipation. The proposed design, however, uses a high threshold voltage for the tail transistor in the preamplifier, which limits the active time of the tail-transistor preamplifier taking average power to avery low level without loss of performance. Furthermore, the latch part of the

comparatorisoptimizedverymuchasalow-power structure tomaximizetheoverall energyefficiencyofthecircuit. This way, one can trade performance with power and energy efficiency. Thustheproposed architecture of the comparator is expected to be suitable for applications in which power consumption is critical concerned, such as portable battery-operated devices.

The dynamic comparator design uses 130 nm CMOS technology and has an input-referred noise level of 290  $\mu V.$  Thislownoiselevelmakesthecomparatorhighlysuitable for analog-to-digital converters (ADCs) requiring up to 11-bit resolution, operating at supply voltage of 1.2 V. The compact design and low power consumption of the comparator make it particularly advantageous for portable and battery-powered devices, where high-resolution signal processing is essential without compromising energy efficiency. This architecture demonstrates an excellent balance between performance, noise reduction, and power efficiency, making it a strong candidate for use in high-resolution, low-power ADCs in modern electronic systems.

# **IV.REFERENCES**

- 1.Schinkel, Daniel, et al. "A double-tail latch-type voltage sense amplifierwith 18ps setup+ hold time." 2007 IEEE international solid-state circuitsconference. Digest of technical papers. IEEE, 2007.

- 2. Kobayashi,Tsuguo,etal."A current-controlledlatch senseamplifieranda static power-saving input buffer for low-power architecture." IEICEtransactions on electronics 76.5 (1993): 863-867.

- 3. Montanaro, James, etal. "A160-mhz, 32-b, 0.5-wCMOSRISC microprocessor." IEEE Journal of Solid-State Circuits 31.11 (1996): 1703-1714.

- 4. Babayan-Mashhadi, Samaneh,and Reza Lotfi. "Analysisand design of alow-voltagelow-power double-tail comparator."IEEE transactions on verylarge scale integration (vlsi) systems 22.2 (2013): 343-352.

- 5. Xu, Hao, and Asad A. Abidi. "Analysis and design of regenerative comparators for low offset and noise." IEEE Transactions on Circuits and Systems I: Regular Papers 66.8 (2019): 2817-2830.

- 6. Malki,Badr,etal."A complementary dynamicresidueamplifier for a 67dB SNDR1.36 mW 170 MS/spipelined SAR ADC." ESSCIRC 2014-40th EuropeanSolidStateCircuitsConference(ESSCIRC).IEEE,2014.

- 7. Wang, Yao, et al. "Low-power high-speed dynamic comparator using anew regenerative stage."2018 IEEE International Conference on ElectronDevices and Solid State Circuits (EDSSC). IEEE, 2018.

- 8. Baghel, Shivam Singh, and D.K. Mishra. "Designand analysis of double-tail dynamic comparator for flash ADCs." 2018 International Conference on Circuits and Systems in Digital Enterprise Technology (ICCSDET). IEEE, 2018.

- 9. Ni, Ya-Bo, et al. "A high-speed dynamic comparator with low-powersupply voltage." 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT). IEEE, 2018.

- 10. Rezapour, Ali, et al. "Lowpowerhighspeeddynamic comparator." 2018 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2018.